In recent years, with the high functionality and performance of various electronic systems, the current consumption of ICs has become larger and larger. On the other hand, the high functionality of the IC promotes the refinement of the internal structure, which results in the drop the withstand voltage of the IC and the power supply voltage.The trend in recent years demands the reduction of voltage fluctuations, and at the mean time, the increase of IC current consumption. Therefore, there is a need to further reduce another factor - impedance.

In this guide, we will introduce technical support to reduce the power line impedance and reduce the number of decoupling capacitors by using a PI (power integrity) simulation to convert a 2-terminal MLCC (multilayer ceramic chip capacitor) to a low ESL product.

As the supply voltage drops, it is increasingly important to reduce the impedance of the power line.To suppress voltage fluctuations, it is necessary to lower the impedance. To achieve the required impedance characteristics in the case where the substrate size and the mounting area are severely limited, TDK proposes a scheme for reducing the number of decoupling capacitors by replacing it with a low ESL product.

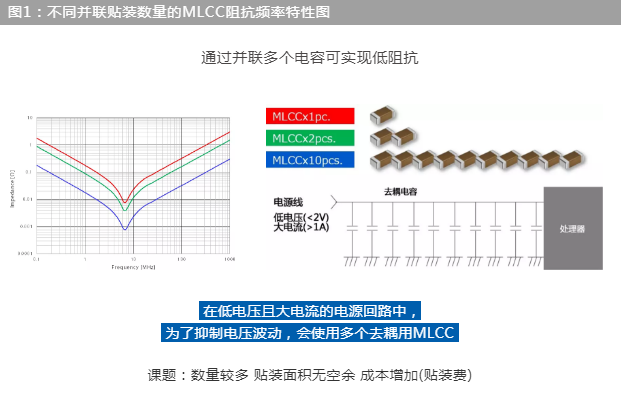

Decoupling capacitors for low voltage/high current power lines

In recent years, with the high functionality and high-speed operation of electronic equipment systems, the characteristics of power lines (PI: power integrity) for digital ICs within the system have become increasingly important.

The key to increasing PI is to reduce the impedance of the power line. Therefore, a large number of MLCCs are used as decoupling capacitors in the power line.

However, with the miniaturization of mounting, the restrictions on the substrate size and the mounting area have become stricter, and it has been rare to mount a large amount of necessary MLCC in order to obtain desired impedance characteristics.

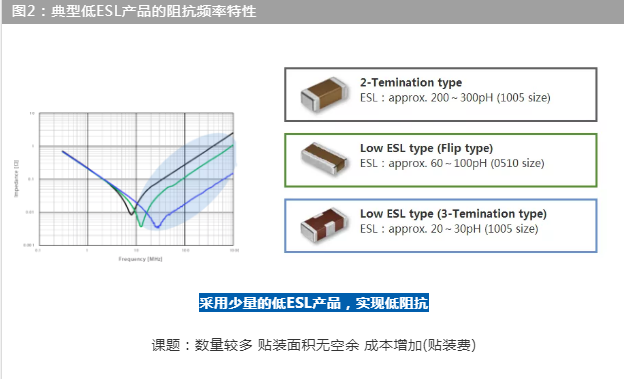

Low impedance with a small number of low ESL products

Therefore, TDK recommends using low ESL capacitors to reduce the number of decoupling capacitors and reduce the mounting area. The low ESL type capacitor is a low inductance component (ESL) product that achieves low impedance from low frequency band to high frequency band. Therefore, the impedance characteristics which can only be realized by a large number ofconventional type of capacitors can be realized by applying a small amount of low ESL type capacitors.

The substrate wiring pattern is also part of the circuit

In addition to the optimal selection and structuring of the decoupling capacitors, the pattern design of the mounting substrate also plays an important role in the low impedance of the power supply line. There is a resistance component, a parasitic inductance, and a stray capacitance in the conductor pattern and the via hole of the mounting substrate. In the impedance design of the power supply line, the electrical component of the substrate itself also needs to be taken into consideration as a part of the impedance component in the substrate pattern design.

TDK performs PI simulation verification by importing the mounting substrate information to provide technical support for optimal power line design.

In line with the substrate type, mounting surface / IC Pin Layout / peripheral component layout and other mounting substrate structure, the best choice of capacitor type, quantity structure, substrate line style, component layout etc. can be provided.

In general, various constraints arise as the substrate design progresses. Therefore, to provide sufficient support for customer development, the best time for effective use is at the initial verification stage which happens before the substrate pattern design.

For example, before the official start of the substrate pattern design, we can also verify and propose the required number of MLCC decoupling capacitors, the allowable distance when the MLCC cannot be placed near the IC, and so on. Therefore, if you have problems with the power line design, please contact us as early as possible at the early stages of development.